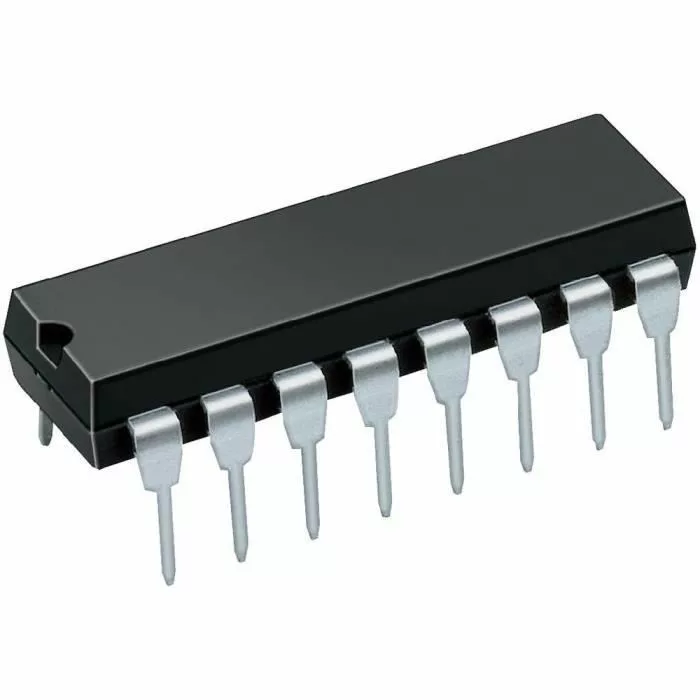

Circuit intégré 74LS73 DIP-14 : Améliorez vos projets électroniques avec fiabilité

Découvrez le Circuit intégré 74LS73 DIP-14

Si vous recherchez un composant électronique fiable et performant, le Circuit intégré 74LS73 DIP-14 est un choix incontournable. Conçu pour répondre aux exigences les plus élevées en matière d’électronique, ce circuit intégré est idéal pour une variété d’applications électriques.

Pourquoi choisir le Circuit intégré 74LS73 DIP-14 ?

- Fiabilité inégalée : Le 74LS73 DIP-14 est reconnu pour sa stabilité et sa durabilité, garantissant un fonctionnement sans faille de vos projets.

- Hautes performances : Avec ses caractéristiques techniques avancées, ce circuit intégré offre des performances optimales, répondant aux besoins des applications les plus exigeantes.

- Facilité d’intégration : Grâce à son format DIP-14 standard, il est simple à intégrer dans vos conceptions électroniques existantes.

- Polyvalence : Le 74LS73 DIP-14 est adapté à une large gamme d’utilisations, des projets amateurs aux applications professionnelles.

Ne cherchez plus, le Circuit intégré 74LS73 DIP-14 est l’élément essentiel à tout projet électronique réussi. Procurez-vous le vôtre dès aujourd’hui et laissez votre créativité s’exprimer !

Caractéristiques techniques du Circuit intégré 74LS73 DIP-14 :

- Type de circuit : TTL

- Nombre de broches : 14

- Tension d’alimentation : 5V

- Température de fonctionnement : -40 °C à 85 °C

- Gamme de fréquence : 0 à 25 MHz

Mots-clés : Composant électronique, Circuit intégré, 74LS73 DIP-14, Electronique, Electricité.

Anonyme (client confirmé) –

Facile à utiliser et très performant. Merci !

Store manager Postmaster –

Heureux de savoir que vous êtes satisfait. Merci pour votre recommandation !

Emna Chakroun (client confirmé) –

Store manager Postmaster –

Meriem Masmoudi (client confirmé) –

Très bonne expérience d’achat, je commanderai à nouveau.

Store manager Postmaster –

Bilel Mhiri (client confirmé) –

Correct pour le prix, mais pas exceptionnel.

Store manager Postmaster –

Nous apprécions votre avis et prenons note de vos remarques pour progresser.