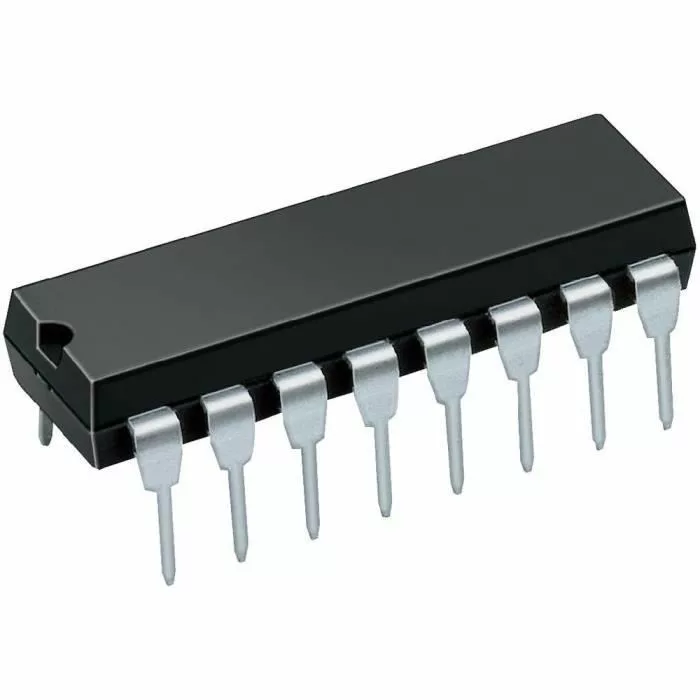

Circuit intégré 74LS95 DIP-14 : Augmentez vos projets électroniques avec fiabilité

Si vous recherchez un composant électronique essentiel pour vos projets, le Circuit intégré 74LS95 DIP-14 est un choix incontournable. Conçu pour offrir une performance optimale et une fiabilité à toute épreuve, ce circuit intégré est la solution idéale pour vos besoins en électricité et électronique.

Fonctionnalités clés du Circuit intégré 74LS95 DIP-14 :

- Hautes performances : bénéficiez d’une vitesse de fonctionnement rapide et efficace.

- Fiabilité exceptionnelle : assurez-vous que votre projet fonctionne de manière stable et constante.

- Facile à intégrer : sa forme DIP-14 permet une intégration simple sur vos circuits imprimés.

Que vous soyez un passionné d’électronique ou un professionnel du domaine, le Circuit intégré 74LS95 DIP-14 répondra à vos attentes les plus exigeantes. Ne laissez pas passer l’opportunité d’améliorer vos réalisations électroniques avec ce composant de qualité supérieure.

Caractéristiques techniques du Circuit intégré 74LS95 DIP-14 :

- Type de boîtier : DIP-14

- Tension d’alimentation : 4,75 V à 5,25 V

- Température de fonctionnement : -55°C à 125°C

- Nombre de broches : 14

- Technologie : TTL

N’hésitez plus et procurez-vous dès aujourd’hui le Circuit intégré 74LS95 DIP-14 pour des performances électroniques inégalées dans tous vos projets.

Mots-clés : Composant électronique, Circuit intégré, Fiabilité, Performance, Projet électronique.

Parlant de composants électroniques, vous pourriez être intéressé par Circuit intégré qui est un élément clé dans la fabrication de dispositifs électroniques. De plus, vous pourriez également explorer le monde de la Électricité pour mieux comprendre les principes fondamentaux qui sous-tendent le fonctionnement de votre projet électronique.

Aya Ben Hassen (client confirmé) –

Not work as promised

Store manager Postmaster –

Merci pour votre retour, nous allons enquêter et améliorer ce point.

Anonyme (client confirmé) –

Store manager Postmaster –

Houssem Ben Hassen (client confirmé) –

Un plaisir d’acheter sur ce site, tout était parfait.

Store manager Postmaster –

Sami Kallel (client confirmé) –

Très bonne expérience d’achat, je commanderai à nouveau.

Store manager Postmaster –

Nous vous remercions pour votre confiance et votre soutien. À très bientôt sur Didactico.